UG0596

UG0596

Guía del usuario

Estimador de potencia RTG4 FPGA

UG0596 RTG4 FPGA Software de estimación de potencia

Microsemi no ofrece ninguna garantía con respecto a la información contenida en este documento o la idoneidad de sus productos y servicios para un propósito particular, ni Microsemi asume responsabilidad alguna que surja de la aplicación o el uso de cualquier producto o circuito. Los productos vendidos a continuación y cualquier otro producto vendido por Microsemi han sido sujetos a pruebas limitadas y no deben usarse junto con equipos o aplicaciones de misión crítica. Las especificaciones de rendimiento se consideran confiables, pero no se verifican, y el Comprador debe realizar y completar todas las pruebas de rendimiento y de otro tipo de los productos, solos y junto con, o instalados en, cualquier producto final. El Comprador no se basará en los datos y especificaciones o parámetros de rendimiento proporcionados por Microsemi. Es responsabilidad del Comprador

determinar de forma independiente la idoneidad de cualquier producto y probarlo y verificarlo. La información proporcionada por Microsemi a continuación se proporciona "tal cual, dónde está" y con todas las fallas, y todo el riesgo asociado con dicha información es totalmente del Comprador. Microsemi no otorga, explícita o implícitamente, a ninguna de las partes ningún derecho de patente, licencia o cualquier otro derecho de propiedad intelectual, ya sea con respecto a dicha información en sí misma o cualquier cosa descrita en dicha información. La información proporcionada en este documento es propiedad de Microsemi, y Microsemi se reserva el derecho de realizar cambios en la información de este documento o en cualquier producto y servicio en cualquier momento sin previo aviso.

Acerca de Microsemi

Microsemi, una subsidiaria de propiedad absoluta de Microchip Technology Inc. (Nasdaq: MCHP), ofrece una cartera integral de soluciones de sistemas y semiconductores para los mercados aeroespacial y de defensa, comunicaciones, centro de datos e industrial.

Los productos incluyen circuitos integrados analógicos de señal mixta de alto rendimiento y resistentes a la radiación, FPGA, SoC y ASIC; productos de administración de energía; dispositivos de temporización y sincronización y soluciones de tiempo preciso, estableciendo el estándar mundial para el tiempo; dispositivos de procesamiento de voz; soluciones de radiofrecuencia; componentes discretos; soluciones empresariales de almacenamiento y comunicación, tecnologías de seguridad y anti-t escalablesamper productos; soluciones de Ethernet; Midspans e IC de alimentación a través de Ethernet; así como capacidades y servicios de diseño personalizados. Obtenga más información en www.microsemi.com.

Historial de revisiones

El historial de revisiones describe los cambios que se implementaron en el documento. Los cambios se enumeran por revisión, comenzando con la publicación más reciente.

1.1 Revisión 2.0

Actualizado para RTG4 Power Estimator v6a.

1.2 Revisión 1.0

Esta fue la primera publicación de este documento.

Estimador de potencia RTG4 FPGA

2.1 Introducción

Esta guía del usuario describe el Estimador de potencia RTG4™ para las familias de dispositivos RTG4 Field Programmable Gate Array (FPGA). La estimación temprana de energía ayuda a los diseñadores a definir la arquitectura dentro del presupuesto de energía mediante la aplicación de estrategias de ahorro de energía. También ayuda a los diseñadores de placas a diseñar y seleccionar las fuentes de alimentación y el disipador de calor. El libro de trabajo Power Estimator se usa para estimar el consumo de energía desde el concepto de diseño inicial hasta la implementación del diseño. También proporciona detalles sobre el análisis térmico y los factores que contribuyen al consumo de energía. Los recursos del dispositivo, la frecuencia operativa, los recursos del reloj, las velocidades de alternancia y muchos otros parámetros se ingresan en el libro de trabajo de Power Estimator.

Estos parámetros luego se combinan con los modelos de potencia para estimar la potencia. Los modelos de potencia se basan en simulación o datos de dispositivos caracterizados.

La precisión de la estimación de potencia depende de los datos ingresados en el libro de trabajo. Por lo tanto, asegúrese de que se ingresen datos realistas en el diseño. La potencia real depende en gran medida del diseño RTL real, el lugar y la ruta y las condiciones de operación. El resultado de Power Estimator es una estimación temprana del consumo de energía en lugar de medirlo. Utilice la herramienta SmartPower en el software Libero® System-on-Chip (SoC) para obtener estimaciones de potencia precisas y detalladas para los diseños después de colocar y enrutar. La potencia debe medirse durante el funcionamiento del dispositivo.

2.1.1 Características

El Estimador de potencia RTG4 tiene las siguientes características:

- Estimación del consumo de energía desde la fase de concepto de diseño hasta la implementación.

- Interfaz gráfica de usuario (GUI) integrada en una hoja de trabajo para inicializar el Power Estimator y para I/O Bank voltagy configuraciones.

- Estimación de potencia de los modos de potencia Activo y Standby.

- Estimación de potencia mediante escenarios.

- Hoja de trabajo separada para las funciones del dispositivo y también un subtotal de energía consumida por cada función del dispositivo.

- Cálculo de la temperatura de unión y soporte térmico de entrada.

2.2 Documentación adicional

- Resumen del producto RTG4 FPGA

- Descripciones de pines RTG4 FPGA

- Guía del usuario de RTG4 FPGA Fabric

- Guía del usuario de interfaces DDR de alta velocidad RTG4 FPGA

- Guía del usuario de interfaces seriales de alta velocidad RTG4 FPGA

- Guía del usuario de recursos de sincronización de RTG4 FPGA

- Guía del usuario de Libero SoC

2.3 Estimador de potencia de lanzamiento

Esta sección contiene las siguientes subsecciones:

- Requisitos del sistema, página 3

- Descarga de Power Estimator y activación de macros, página 3

- Requisitos mínimos de entrada, página 5

2.3.1 Requisitos del sistema

- El libro de trabajo de Power Estimator requiere Microsoft Excel. La Tabla 1 muestra el software compatible.

- Sistema operativo Windows.

Tabla 1 • Software compatible

Software compatible

Microsoft Excel 2003

Microsoft Excel 2007

Microsoft Excel 2010

Microsoft Excel 2013

Nota: Los editores de hojas de cálculo de OpenOffice y Google Docs no son compatibles.

2.3.2 Descarga de Power Estimator y activación de macros

El libro de trabajo de Power Estimator para la última versión de los dispositivos RTG4 se puede descargar desde:

https://www.microsemi.com/document-portal/doc_download/1244030-rtg4-power-calculator

El libro de trabajo de Power Estimator tiene varias macros integradas. De forma predeterminada, el nivel de seguridad de macros en el software de Microsoft Excel está establecido en Alto. Las macros se desactivan automáticamente si el nivel de seguridad de macros se establece en Alto. Asegúrese de que la configuración de Microsoft Excel permita la ejecución de macros para que el libro de trabajo de Power Estimator funcione correctamente.

Las siguientes secciones describen cómo cambiar la configuración de seguridad de macros en diferentes versiones del software Microsoft Excel:

- Microsoft Excel 2003, página 3

- Microsoft Excel 2007, página 3

- Microsoft Excel 2010 y 2013, página 5

2.3.2.1 Microsoft Excel 2003

- Abra el Power Estimator Excel file y seleccione Herramientas > Macro > Seguridad en el menú principal.

Figura 1 • Configuración del nivel de seguridad de macros en Microsoft Excel 2003

- En el cuadro de diálogo Seguridad de macros, haga clic en la pestaña Nivel de seguridad y seleccione Medio. Haga clic en Aceptar.

- Cerrar el Estimador de potencia file y vuelva a abrirlo.

- Haga clic en Habilitar macros cuando se le solicite habilitar macros.

2.3.2.2 Microsoft Excel 2007

- Abra el Power Estimator Excel file y haga clic en el botón de Office en la esquina superior izquierda.

- Haga clic en Opciones de Excel.

Figura 2 • Configuración del nivel de seguridad de macros en Microsoft Excel 2007

- Haga clic en Centro de confianza en el panel izquierdo.

- Haga clic en Configuración del Centro de confianza….

- En la ventana del Centro de confianza, haga clic en Configuración de macros en el panel izquierdo. Seleccione Deshabilitar todas las macros con notificación y haga clic en Aceptar.

- Cerrar el Estimador de potencia file y vuelva a abrirlo.

- Aparece una notificación de advertencia de seguridad debajo de la cinta de opciones de Office. Haga clic en Opciones.

- Elija Habilitar este contenido en la ventana Opciones de seguridad de Microsoft Office.

2.3.2.3 Microsoft Excel 2010 y 2013

- Abra el Power Estimator Excel file.

- Haga clic en el File pestaña y haga clic en Opciones.

Figura 3 • Configuración del nivel de seguridad de macros en Microsoft Excel 2010 y 2013

- Haga clic en Centro de confianza en el panel izquierdo.

- Haga clic en Configuración del Centro de confianza….

- En la ventana del Centro de confianza, haga clic en Configuración de macros en el panel izquierdo. Seleccione Deshabilitar todas las macros con notificación y haga clic en Aceptar.

- Cerrar el Estimador de potencia file y vuelva a abrirlo.

- Aparece una notificación de advertencia de seguridad debajo de la cinta de opciones de Office. Haga clic en Opciones.

- Elija Habilitar este contenido en la ventana Opciones de seguridad de Microsoft Office.

2.3.3 Requisitos mínimos de entrada

La estimación de la potencia para los dispositivos RTG4 depende en gran medida de la cantidad de lógica presente en el FPGA Fabric.

Los siguientes son los requisitos mínimos de entrada para una estimación de potencia razonablemente precisa:

- Seleccione un dispositivo adecuado con las condiciones de funcionamiento adecuadas.

- Estimación adecuada de los recursos de FPGA Fabric (por ej.ample, flip-flops, LUT, LSRAM, uSRAM, MACC y E/S).

- Estimación adecuada de interfaces seriales y DDR de alta velocidad.

- Reloj del sistema y dominio del reloj.

- Alternar velocidades de lógica y E/S.

- Habilite, escriba y lea velocidades para RAM.

2.4 Libro de trabajo de Excel de Power Estimator

Esta sección describe cada hoja de trabajo del libro de trabajo de Excel RTG4 Power Estimator. Hay hojas de trabajo separadas para las características del dispositivo disponibles. Además, está disponible un subtotal de energía consumida por cada característica del dispositivo. Se pueden ingresar los detalles de uso y actividad de los diferentes recursos disponibles en el dispositivo RTG4 objetivo (por ej.ample, flip-flops, LUT, LSRAM, uSRAM, MACC, E/S, interfaces serie y DDR de alta velocidad, reloj del sistema y dominio del reloj, velocidades de alternancia de lógica y E/S). La sección Resumen de energía en la hoja de trabajo Resumen proporciona la energía total y el desglose de energía por riel y tipo de recurso.

Esta sección contiene las siguientes subsecciones:

- Codificación de celdas por colores, página 6

- Caudal recomendado, página 6

2.4.1 Codificación por colores de las celdas

El libro de trabajo de Excel RTG4 Power Estimator tiene varias hojas de trabajo. Las celdas de cada hoja de trabajo están codificadas por colores para simplificar la entrada de datos y review.

La Tabla 2 enumera los colores y la descripción de las celdas.

Tabla 2 • Codificación de colores de las celdas

| Color de celda | Acción del usuario | Descripción |

| Editable | El usuario puede ingresar datos | |

| no editable | El usuario no puede ingresar datos | |

| Sólo lectura | Valores calculados | |

| Sólo lectura | Valores de resumen | |

| Sólo lectura | Error |

2.4.2 Flujo recomendado

2.4.2.1 Paso – 1: Configuración

Seleccione el dispositivo, el paquete, el grado de temperatura, la condición de funcionamiento y la configuración de las entradas térmicas.

2.4.2.2 Paso – 2: Configuración del modo activo

Configure la información específica del diseño que se utiliza para calcular la potencia dinámica.

- Componentes de la estructura FPGA:

- Configure los componentes de FPGA Fabric y sus frecuencias operativas.

- E/S:

- Configure la tecnología de E/S y sus frecuencias de funcionamiento.

- Bloques Integrados (SERDES y FDDR):

- Configure los subsistemas SERDES y DDR con la configuración adecuada.

2.4.2.3 Paso – 3: Escenarios

Opcional: actualice el porcentajetage de tiempo que el dispositivo debe estar en un modo determinado durante su tiempo de funcionamiento (por ejemplo, el 50% del tiempo Activo y el 50% en Standby).

2.4.2.4 Paso – 4: Resumen de estimación de potencia

La sección de resumen de energía en la hoja de trabajo Resumen proporciona la energía total y su desglose en función de las fuentes de energía y los rieles. La potencia total para el escenario se describe en el Paso 3: Escenarios, página 22.

Las siguientes secciones describen estos pasos en detalle:

- Paso – 1: Configuración, página 7

- Paso – 2: Configuración del modo activo, página 10

- Paso – 3: Escenarios, página 22

- Paso – 4: Resumen de estimación de potencia, página 23

2.5 Paso – 1: Configuración

La Figura 4 muestra la sección Configuración en la hoja de trabajo Resumen.

Figura 4 • Sección de configuración en la hoja de trabajo de resumen

La Tabla 3 muestra la configuración de las entradas generales y térmicas en la sección Configuración de la hoja de trabajo Resumen. Asegúrese de seleccionar el dispositivo con las condiciones de funcionamiento adecuadas.

| Parámetros | Descripción |

| Configuración general | |

| Familia | RTG4 |

| Dispositivo | Seleccione el dispositivo. Los siguientes dispositivos son compatibles: • RT4G150L |

| Paquete | Seleccione el paquete. |

| Rango | Seleccione el grado del producto. Los siguientes grados están disponibles. • E Militar Grado de temperatura para diferentes rangos: • E Militar (-55 °C a 125 °C) |

| Volumen principaltage | Volumen de suministro principaltagmi (1.2 V) |

| Proceso | Seleccione el proceso. Las siguientes condiciones están disponibles: • Típico El proceso da cuenta de las variaciones del proceso de fabricación que afectan la disipación de energía. Típico utiliza factores de disipación de energía promedio para su diseño. Vol.tage y la temperatura se controlan independientemente del proceso. |

| Estado de datos | Avanzado: Información inicial estimada basada en simulación, otros productos, dispositivos o grados de velocidad. Esta información se puede utilizar como estimaciones, pero no para la producción. Preliminar: Información basada en simulación y/o caracterización inicial. Se cree que la información es correcta, pero es posible que se produzcan cambios. Producción: Información que se considera definitiva. |

| Entradas Térmicas | |

| Temperatura de unión Tj (°C) Nota: Los datos térmicos aún no están disponibles. Solo se admite la opción TJ ingresada por el usuario. |

Introduzca la temperatura de unión del dispositivo. Este campo está disponible solo cuando se selecciona la opción TJ ingresada por el usuario. En este caso, otros campos de entrada térmica están deshabilitados. Cuando se selecciona la opción TJ estimado, la temperatura de la unión se calcula en función de las entradas térmicas ingresadas. |

| Temperatura ambiente Ta (°C) | Introduzca la temperatura del aire que rodea el dispositivo. Este campo está disponible solo si se selecciona la opción TJ estimado. Los rangos de temperatura válidos son: • E Militar: -55 °C a 125 °C Cuando se selecciona la opción Estimado Theta JA, este campo se usa para calcular la temperatura de la unión en función de la resistencia térmica y la disipación de potencia. Cuando se selecciona la opción Custom Theta JA, este campo se utiliza para calcular la temperatura de la unión en función de la qJA efectiva y la disipación de energía. |

| qJA efectivo | Resistencia térmica efectiva. El dispositivo, el paquete, el flujo de aire, el disipador de calor y el modelo de placa seleccionados por el usuario se utilizan con datos de caracterización y simulación para calcular la resistencia térmica efectiva. Para ingresar un Theta JA efectivo personalizado, seleccione Custom Theta JA e ingrese un valor, para tener en cuenta las condiciones no cubiertas por las opciones disponibles o donde se ha realizado un modelado térmico más extenso. Los siguientes campos están deshabilitados cuando se selecciona Theta JA personalizado y se habilita Theta JA estimado: • Disipador de calor E • E Flujo de aire • E Personalizada qSA (°C/W) • Modelo Térmico de Tablero E |

| Disipador de calor | Seleccione una de las siguientes opciones: • Ninguna • Personalizado • 10 mm-Bajo Profile • 15 mm-Medio Profile • 20 mm de altura Profile Este campo está habilitado solo cuando se seleccionan las opciones Estimado TJ y Estimado Theta JA. |

| Flujo de aire | Seleccione un flujo de aire ambiental en metros por segundo (m/s): • 1.0 m/s • 2.5 m/s Este campo está habilitado solo cuando se seleccionan las opciones Estimado TJ y Estimado Theta JA. La temperatura de la unión se reduce si aumenta el flujo de aire ambiental. |

| QSA personalizado (°C/W) | Si se selecciona un disipador de calor personalizado, ingrese la resistencia térmica del disipador de calor al ambiente de la hoja de datos del disipador de calor. Este campo está habilitado solo cuando se seleccionan las opciones Estimado TJ y Estimado Theta JA. |

| Modelo Térmico de Tablero | Seleccione una de las siguientes opciones: • Ninguno (Conservador) • JEDEC (2s2p) Este campo está habilitado solo cuando se seleccionan las opciones Estimado TJ y Estimado Theta JA. Si se selecciona la opción Ninguno (Conservador), el modelo térmico asume que no se disipa calor a través de la placa. Si se selecciona la opción JEDEC (2s2p), el modelo térmico asume que las características son de la placa de prueba JEDEC 2s2p especificada en el estándar JESD51-9. |

2.6 Paso – 2: Configuración del modo activo

En esta sección, ingrese información específica del diseño que se puede usar para calcular la potencia dinámica.

Contiene las siguientes subsecciones:

- Asistente para inicializar el estimador de energía, página 10

- Componentes de la estructura FPGA, página 11

- E/S, página 17

- Bloques integrados, página 19

2.6.1 Asistente para inicializar el estimador de energía

La hoja de trabajo Resumen tiene un asistente de estimación de potencia integrado. Haga clic en Inicializar estimador de energía en la parte superior izquierda de la hoja de trabajo para invocar el asistente de Inicializar estimador de energía. Este asistente permite al usuario seleccionar información específica del diseño. Al ejecutar el asistente, completa la hoja de cálculo de Power Estimator con información específica del diseño y estima la potencia para el diseño. Cambie las entradas pobladas del asistente para proporcionar entradas más precisas al Estimador de energía.

La figura 5 muestra el asistente de inicialización del estimador de energía.

Figura 5 • Asistente de estimación de energía

El asistente de Power Estimator proporciona los siguientes campos según la familia de productos seleccionada:

- Departamento de Defensa de los Estados Unidos

Seleccione el tipo de memoria, ancho, ECC, ODT y FDDR_CLK.

La frecuencia máxima de FDDR_CLK es de 333 MHz. - SERDES_IF

Seleccione subsistema PCIE (PCIESS), subsistema no PCIE (NPSS), Protocolo, Número de carriles, reloj AXI/AHB_CLK (PCIe) y Ref Clk Freq. - Tejido FPGA

- Reloj del sistema

Especifique la frecuencia de reloj de Fabric. De forma predeterminada, se establece en 100 MHz. Las entradas válidas están entre 0 y 300 MHz. - Utilización del diseño

Use el menú desplegable en Establecer todos los recursos de estructura FPGA para establecer un porcentajetagValor e para todos los recursos de una sola vez. un porcentajetagEl valor de cada recurso que se utilizará se puede establecer usando la barra deslizante contra los recursos.

Los siguientes son los recursos disponibles:

* Chancletas

* LUT

* USRAM

* LRAM

* MACC - E/S

Seleccione la tecnología de E/S e introduzca el número de entradas y salidas. - Tasa de alternancia predeterminada

Introduzca una tasa de cambio en porcentajetagmi. Esta tasa de alternancia se aplica a todos los módulos lógicos y E/S. - Tasa de habilitación de RAM predeterminada

Ingrese una tasa de habilitación en porcentajetagmi. Esta tasa de habilitación se aplica a uSRAM y LSRAM.

Nota: Cuando el pulgar del control deslizante se mueve entre los puntos finales de la pista del control deslizante, el valor se actualiza en el campo de texto correspondiente.

Para completar la hoja de cálculo de Power Estimator con los valores ingresados, haga clic en Aceptar.

2.6.2 Componentes de la estructura FPGA

Esta sección describe el diseño de información específica para los componentes de FPGA Fabric que se utilizan para calcular la potencia dinámica. El libro de trabajo RTG4 Power Estimator proporciona hojas de trabajo separadas para cada componente de FPGA Fabric. Estas hojas de trabajo se describen en las siguientes subsecciones:

- Reloj, página 11

- Lógica, página 12

- LSRAM, página 13

- uSRAM, página 14

- Bloque matemático, página 15

- CCC, página 16

2.6.2.1 Reloj

Los dispositivos RTG4 solo admiten redes de reloj global. Cada fila de la hoja de cálculo Reloj representa un dominio de reloj independiente.

Introduzca los siguientes parámetros para cada dominio de reloj:

- Nombre

- Frecuencia de reloj (MHz)

- Abanico de distribución

- Tasa de habilitación global

La Figura 6 muestra la hoja de trabajo Reloj.

Figura 6 • Hoja de trabajo del reloj

La Tabla 4 muestra los parámetros que se deben ingresar en la hoja de trabajo Reloj.

Tabla 4 • Parámetros de la hoja de trabajo del reloj

| Parámetros | Descripción |

| Nombre | Introduzca un nombre para cada dominio de reloj (opcional). |

| Frecuencia de reloj (MHz) | Introduzca la frecuencia de reloj del dominio. La frecuencia máxima del FPGA Fabric es de 300 MHz. |

| Abanico de distribución | Ingrese el número de registros y otros elementos síncronos (LSRAM, uSRAM, bloque matemático y E/S) sincronizados. |

| Tasa de habilitación global | Ingrese el porcentaje promediotage de tiempo que la habilitación del reloj es alta para cada dominio de reloj. |

Para obtener más información sobre las redes de reloj de las familias de dispositivos compatibles, consulte RTG4 FPGA Guía del usuario de recursos de reloj.

2.6.2.2 Lógica

Cada fila en la hoja de trabajo de Lógica representa un dominio de reloj separado.

Introduzca los siguientes parámetros para cada dominio de reloj:

- Nombre

- Frecuencia de reloj (MHz)

- Número de registros

- Número de LUT

- Abanico de distribución

- Tasa de cambio

La Figura 7 muestra la hoja de trabajo Lógica.

Figura 7 • Hoja de trabajo de lógica

La Tabla 5 muestra los parámetros que se deben ingresar en la hoja de cálculo Lógica.

Tabla 5 • Parámetros de la hoja de trabajo lógica

| Parámetros | Descripción |

| Nombre | Introduzca un nombre para cada dominio de reloj (opcional). |

| Frecuencia de reloj (MHz) | Introduzca la frecuencia de reloj del dominio. La frecuencia máxima del FPGA Fabric es de 300 MHz. |

| Número de registros | Introduzca el número de registros para cada dominio de reloj. |

| Número de LUT | Ingrese el número de módulos LUT (combinatorios) regulares. |

| Fanout promedio | Ingrese el fanout promedio de las redes impulsadas por los registros y LUT. |

| Tasa de cambio | Ingrese la velocidad de alternancia de las salidas de registro y LUT. |

Para obtener más información sobre el elemento lógico de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGAFabric.

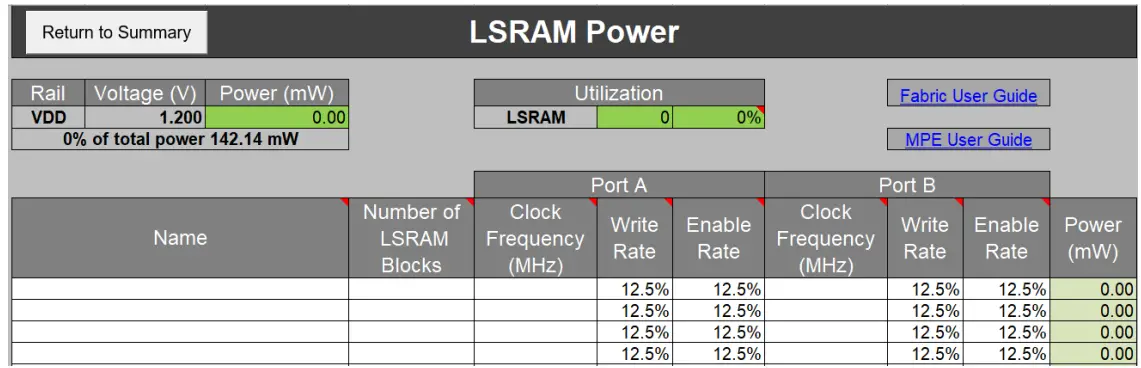

2.6.2.3 LRAM

Cada fila en la hoja de trabajo de LSRAM representa un dominio de reloj separado.

Introduzca los siguientes parámetros para cada dominio de reloj:

- Nombre

- Número de bloques LSRAM

- Puerto A - Frecuencia de reloj (MHz)

- Puerto A: tasa de escritura

- Puerto A: tasa de habilitación

- Puerto B - Frecuencia de reloj (MHz)

- Puerto B: tasa de escritura

- Puerto B: tasa de habilitación

La Figura 8 muestra la hoja de trabajo de LSRAM.

Figura 8 • Hoja de trabajo de LSRAM

La Tabla 6 muestra los parámetros que se deben ingresar en la hoja de trabajo de LSRAM.

Tabla 6 • Parámetros de la hoja de trabajo de LSRAM

| Parámetros | Descripción |

| Nombre | Introduzca el nombre del módulo o dominio de reloj que contiene la LSRAM. |

| Número de bloques LSRAM | Introduzca el número de bloques LSRAM. |

| Puerto A - Frecuencia de reloj (MHz) | Ingrese la frecuencia de reloj para el Puerto A de los bloques LSRAM. Soporta una frecuencia máxima de hasta 300 MHz. |

| Puerto A: tasa de escritura | Ingrese el porcentajetage de tiempo que el puerto A se utiliza para operaciones de escritura. El tiempo restante se utiliza para operaciones de lectura. |

| Puerto A: tasa de habilitación | Ingrese el porcentajetage de tiempo que el puerto A está habilitado. |

| Puerto B - Frecuencia de reloj (MHz) | Ingrese la frecuencia de reloj para el Puerto B de los bloques LSRAM. Soporta una frecuencia máxima de hasta 300 MHz. |

| Puerto B: tasa de escritura | Ingrese el porcentajetage de tiempo que el puerto B se utiliza para operaciones de escritura. El tiempo restante se utiliza para operaciones de lectura. |

| Puerto B: tasa de habilitación | Ingrese el porcentajetage de tiempo que el Puerto B está habilitado. |

Para obtener más información sobre la LSRAM de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGA Fabric.

2.6.2.4 memoria USB

Cada fila en la hoja de trabajo de uSRAM representa un dominio de reloj separado.

Introduzca los siguientes parámetros para cada dominio de reloj:

- Nombre

- Número de bloques uSRAM

- Puerto A: lectura de frecuencia de reloj (MHz)

- Puerto A: tasa de habilitación

- Puerto B: lectura de frecuencia de reloj (MHz)

- Puerto B: tasa de habilitación

- Puerto C: frecuencia de reloj de escritura (MHz)

- Puerto C: tasa de activación

La Figura 9 muestra la hoja de trabajo de uSRAM.

Figura 9 • Hoja de trabajo de uSRAM

La Tabla 7 muestra los parámetros que se deben ingresar en la hoja de trabajo de uSRAM.

Tabla 7 • Parámetros de la hoja de trabajo de uSRAM

| Parámetros | Descripción |

| Nombre | Ingrese el nombre del módulo o dominio de reloj que contiene la uSRAM. |

| Número de bloques uSRAM | Ingrese el número de bloques de uSRAM. |

| Puerto A: lectura de frecuencia de reloj (MHz) | Ingrese la frecuencia de reloj de lectura para el puerto A de los bloques uSRAM. Soporta una frecuencia máxima de hasta 300 MHz. |

| Puerto A: tasa de habilitación | Ingrese el porcentajetage de tiempo que el puerto A está habilitado. |

| Puerto B: lectura de frecuencia de reloj (MHz) | Ingrese la frecuencia de reloj de lectura para el puerto B de los bloques uSRAM. Soporta una frecuencia máxima de hasta 300 MHz. |

| Puerto B: tasa de habilitación | Ingrese el porcentajetage de tiempo que el puerto B está habilitado. |

| Puerto C: frecuencia de reloj de escritura (MHz) | Ingrese la frecuencia de reloj de escritura para el puerto C de los bloques uSRAM. Soporta una frecuencia máxima de hasta 300 MHz. |

| Puerto C: tasa de activación | Ingrese el porcentajetage de tiempo que el puerto C está habilitado. |

Para obtener más información sobre la uSRAM de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGA Fabric.

2.6.2.5 Bloque matemático

Cada fila en la hoja de trabajo del bloque matemático representa un dominio de reloj separado.

Introduzca los siguientes parámetros para cada dominio de reloj:

- Nombre

- Frecuencia de reloj (MHz)

- Número de bloques matemáticos

- Tasa de cambio de datos

La figura 10 muestra la hoja de trabajo del bloque matemático.

Figura 10 • Hoja de trabajo de bloques matemáticos

La Tabla 8 enumera los parámetros que se deben ingresar en la hoja de trabajo del bloque matemático.

Tabla 8 • Parámetros de la hoja de trabajo del bloque matemático

| Parámetros | Descripción |

| Nombre | Ingrese el nombre del módulo o dominio de reloj que contiene el bloque matemático. |

| Frecuencia de reloj (MHz) | Introduzca la frecuencia de reloj del dominio. La frecuencia máxima del bloque matemático es de 300 MHz. |

| Número de bloques matemáticos | Ingrese el número de bloques matemáticos para cada dominio de reloj. |

| Tasa de cambio de datos | Ingrese la tasa promedio de alternancia del bus de datos. |

Para obtener más información sobre el bloque matemático de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGA Fabric.

2.6.2.6 CCC

Los dispositivos RTG4 tienen ocho CCC. Cada CCC permite esquemas de reloj flexibles para la lógica implementada en FPGA Fabric y puede proporcionar el reloj base para bloques IP duros en chip como FDDR y SERDESIF.

Introduzca los siguientes parámetros para cada CCC:

- Nombre

- Frecuencia de reloj de referencia (MHz)

- Frecuencia de salida PLL (MHz)

- Frecuencia de salida1 (MHz)

- Frecuencia de salida2 (MHz)

- Frecuencia de salida3 (MHz)

- Frecuencia de salida4 (MHz)

La figura 11 muestra la sección de energía de CCC en la hoja de trabajo de CCC.

Figura 11 • Sección de potencia del CCC

La Tabla 9 muestra los parámetros que se deben ingresar en la sección de potencia de CCC de la hoja de trabajo de CCC.

Tabla 9 • Parámetros de la sección CCC

| Parámetros | Descripción |

| Nombre | Introduzca el nombre del módulo CCC. |

| Frecuencia de reloj de referencia (MHz) | Introduzca la frecuencia del reloj de referencia. |

| Frecuencia de salida PLL (MHz) | Introduzca la frecuencia de salida de PLL. |

| Frecuencia de salida1 (MHz) | Introduzca la frecuencia de salida1 (GL0/Y0). |

| Frecuencia de salida2 (MHz) | Introduzca la frecuencia de salida2 (GL1/Y1). |

| Frecuencia de salida3 (MHz) | Introduzca la frecuencia de salida3 (GL2/Y2). |

| Frecuencia de salida4 (MHz) | Introduzca la frecuencia de salida4 (GL3/Y3). |

Para obtener más información sobre el CCC de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGA Clocking Resources.

2.6.3 E/S

La información específica del diseño se ingresa en la hoja de trabajo de E/S para las E/S utilizadas para calcular la potencia dinámica.

Cada fila representa una frecuencia de reloj y un dominio de E/S.

Introduzca los siguientes parámetros para cada fila:

- Nombre

- Tipo de banco

- estándar de E/S

- Pines I/P

- Pines O/P

- Pines Bidir

- ODT

- Unidad de salida (mA)

- Carga de salida (pF)

- Reloj (MHz)

- Velocidad de datos

- Tasa de cambio

- Habilitar salida

- Habilitar ODT

La figura 12 muestra la hoja de trabajo de E/S.

Figura 12 • Hoja de trabajo de E/S

La Tabla 10 muestra los parámetros que se deben ingresar en la hoja de trabajo de E/S. La configuración avanzada de E/S, el disparador Schmitt, el preénfasis y la rotación no están visibles de forma predeterminada. Seleccione Mostrar configuración avanzada de E/S para mostrar estas columnas.

Tabla 10 • Parámetros de la hoja de trabajo de E/S

| Parámetros | Descripción | |

| Nombre | Introduzca un nombre para cada E/S, bus o módulo. | |

| Configuración de E/S | Tipo de banco | Seleccione el tipo de banco. Admite los siguientes tipos de bancos: •MSIO •MSIOD •DDRIO |

| estándar de E/S | Seleccione el estándar de E/S apropiado. | |

| Pasadores ARRIBA | Ingrese el número de pines de entrada o par diferencial utilizado para cada E/S, bus o módulo. El par diferencial debe considerarse como un solo pin. | |

| 0/P Pines | Ingrese el número de pines de salida o par diferencial utilizado para cada E/S, bus o módulo. El par diferencial debe considerarse como un solo pin. | |

| Pines Bidir | Ingrese el número de pines bidireccionales o par diferencial utilizado para cada E/S, bus o módulo. El par diferencial debe considerarse como un solo pin. | |

| ODT | Seleccione la impedancia de terminación de entrada en matriz. | |

| Unidad de salida (mA) | Seleccione la corriente de accionamiento de salida. | |

| Carga de salida (pF) | Introduzca la placa y otra capacitancia externa. | |

Tabla 10 • Parámetros de la hoja de trabajo de E/S (continuación)

| Parámetros | Descripción | |

| Actividad de E/S | Reloj (MHz) | Introduzca la frecuencia de reloj del dominio. Soporta una frecuencia máxima de hasta 300 MHz. |

| Velocidad de datos | Para las E/S utilizadas como relojes, seleccione el reloj como Velocidad de datos. Para otros, seleccione datos. | |

| Tasa de cambio | Ingrese el porcentaje promediotage de entrada, salida y alternancia de pines bidireccionales. | |

| Habilitar salida | Ingrese el porcentajetage de los pines de salida de tiempo están habilitados. Para E/S bidireccionales, los pines de entrada están activos cuando los pines de salida están deshabilitados. |

|

| Habilitar ODT | Habilitar ODT solo es aplicable: •Para entradas DDRIO y pines bidireccionales (si están conectados para FDDR o MDDR) •Para los estándares: LPDDR, SSTL18 y SSTL15 •Si ODT está habilitado |

|

Para obtener más información sobre las E/S de las familias de dispositivos compatibles, consulte la Guía del usuario de RTG4 FPGA Fabric.

2.6.4 Bloques incorporados

Se ingresa información específica de diseño para bloques integrados (SERDES y FDDR) para calcular la potencia dinámica. Esta sección contiene las siguientes subsecciones:

- SERDES, página 19

- FDDR, página 21

2.6.4.1 SERDES

Los dispositivos RTG4 tienen hasta 6 bloques SERDES (2 PCIESS y 4 NPSS). Depende del dispositivo seleccionado. Cada fila en la hoja de cálculo SERDES representa un carril SERDES único (X1) o múltiple (X2/X4).

Ingrese los siguientes parámetros para cada bloque SERDES:

- Nombre

- Ubicación

- Protocolo

- Numero de carriles

- Velocidad (Gbps)

- PCIe F AXI/AHB (MHz)

- Velocidad de datos (Mbps)

La Figura 13 muestra la hoja de trabajo SERDES.

Figura 13 • Planilla SERDES

La Tabla 11 muestra los parámetros a ser ingresados en la planilla SERDES.

Tabla 11 • Parámetros de la hoja de trabajo SERDES

| Parámetros | Descripción |

| Nombre | Introduzca un nombre para cada bloque SERDES. El nombre es opcional. Cada bloque SERDES se puede configurar como carriles X1, X2 o X4. Las configuraciones pueden ser: •Cuatro X1 •dos X2, o •simple X4 Dependiendo de la configuración de carriles en el bloque SERDES, el número de filas varía. |

| Ubicación | Seleccione la ubicación SERDES. Cada SERDES puede utilizar hasta 4 carriles y depende del dispositivo seleccionado. Cuando se selecciona NPSS, solo los protocolos que no son PCIe (XAUI y EPCS) están disponibles en la columna de protocolo. Cuando se selecciona PCIESS, todos los protocolos (PCIe, XAUI y EPCS) están disponibles. |

| Protocolo | Seleccione el protocolo. Admite los protocolos PCIe, XAUI y EPCS. La Figura 14 muestra la lista de velocidades admitidas cuando se elige el protocolo EPCS. La velocidad personalizada y el ancho de datos se pueden seleccionar en la lista desplegable Tasa de datos (Mbps). La velocidad de VCO y las frecuencias de interfaz de FPGA se completan en función de la velocidad de datos seleccionada. |

| Numero de carriles | Seleccione el número de carriles. Es compatible con X1, X2 y X4. |

| Velocidad (Gbps) | Seleccione la tasa de datos para el protocolo seleccionado. |

| PCIe F AXI/AHB (MHz) | Introduzca la frecuencia de reloj de la interfaz AXI/AHB. Soporta una frecuencia máxima de hasta 200 MHz. |

| Velocidad de datos (Mbps) | Seleccione la velocidad personalizada y el ancho de datos. Este campo está habilitado solo cuando se selecciona el protocolo EPCS. |

| Frecuencia de reloj de referencia (MHz) | Este es un valor fijo para todos los protocolos excepto la velocidad personalizada de EPCS. En este caso, ingrese cualquier valor entre 100 MHz y 160 MHz. |

| Tasa de VCO (MHz) | Valor fijo de solo lectura para todos los protocolos excepto la velocidad personalizada de EPCS. Los valores mostrados se calculan y actualizan en función de la frecuencia del reloj de referencia y la tasa de datos. |

Figura 14 • Velocidad EPCS personalizada

Para obtener más información sobre SERDES de las familias de dispositivos compatibles, consulte la Guía del usuario de interfaces seriales de alta velocidad RTG4 FPGA.

2.6.4.2 FDDR

La Figura 15 muestra la sección de potencia de FDDR en la hoja de trabajo de FDDR. Introduzca los siguientes parámetros para FDDR:

- Nombre

- FAXI/AHB (MHz)

- Multiplicador de reloj DDR

Figura 15 • Sección de potencia FDDR

La Tabla 12 muestra los parámetros que se deben ingresar en la sección Potencia de FDDR de la hoja de trabajo de FDDR.

Tabla 12 • Parámetros de la sección de potencia FDDR

| Parámetros | Descripción |

| Nombre | Introduzca el nombre del módulo que contiene FDDR. |

| FAXI/AHB (MHz) | Introduzca la frecuencia de reloj de la interfaz AXI/AHB. Soporta una frecuencia máxima de hasta 200 MHz. |

| Multiplicador de reloj DDR | Seleccione el factor de multiplicación de frecuencia de DDR. La frecuencia de reloj DDR (FDDR_CLK) debe ser inferior a 334 MHz (por ej.ampes decir, si F AXI/AHB es 167, el multiplicador de reloj DDR no debe ser superior a F AXI/AHB*2). |

Para obtener más información sobre FDDR, consulte la Guía del usuario de interfaces DDR de alta velocidad RTG4 FPGA.

2.7 Paso – 3: Escenarios

En esta sección, ingrese los modos operativos del dispositivo durante su tiempo operativo, por ejemplo, 50% del tiempo Activo y 50% en Standby. Ingrese el porcentajetage de tiempo que se espera que el dispositivo esté en los modos Activo y En espera. Esta sección está disponible en la hoja de trabajo Resumen. Es opcional proporcionar estos detalles.

La Figura 16 muestra la sección Modos y escenarios en la hoja de trabajo Resumen.

Figura 16 • Sección Modos y Escenarios

2.8 Paso – 4: Resumen de estimación de potencia

La sección Resumen de energía proporciona la energía total y el desglose de energía en función de las fuentes de energía y los rieles. También proporciona el resumen del Margen Térmico (Ta Máxima y Potencia Máxima).

La Figura 17 muestra las secciones Resumen actual, Resumen de energía y Modos y escenarios en la hoja de trabajo Resumen.

Figura 17 • Hoja de trabajo de resumen

Nota: La Tabla 13 muestra el volumen de riel aceptabletage rango.

Tabla 13 • Volumen ferroviario aceptabletage Rango

| Nombre del carril | Volumentage Rango (V) | |

| Mínimo | Máximo | |

| VDD | 1.14 | 1.26 |

| VDDI 1.2 | 1.14 | 1.26 |

| VDDI 1.5 | 1.425 | 1.575 |

| VDDI 1.8 | 1.71 | 1.89 |

| VDDI 2.5 | 2.375 | 2.625 |

| VDDI 3.3 | 3.15 | 3.45 |

| SERDES J011_L[0123LVDDA10 | 1.14 | 1.26 |

| SERDES JOILL[0123]_VDDAPLL | 2.375 | 2.625 |

| PLL_VDDA (3.3 V)1 | 3.135 | 3.465 |

| SERDES VDDI | 1.14 | 3.45 |

| Vicepresidente | 3.135 | 3.465 |

1. El suministro analógico PLL incluye SERDES_x_PLL_VDDA (x: 0 a 6), FDDR_x_PLL_VDDA (x: 0 a 2) y CCC_x_PLL_VDDA (x = NE0, NE1, NW0, NW1, SW0, SW1, SE0, SE1).

La selección de estándares SERDES_REFCLK (tipo de banco) y IO en la pestaña IO depende del volumen de riel SERDES_VDDI.tage en la pestaña Resumen.

Nota: Puede cambiar el volumen de riel SERDES_VDDItage de la tabla Rail Breakdown en la pestaña Summary. Los siguientes son los rangos aplicables:

- [1.14, 1.26] para 1.2 V

- [1.425, 1.575] para 1.5 V

- [1.710, 1890] para 1.8 V

- [2.375, 2.625] para 2.5 V

- [3.15, 3.45] para 3.3. V

Figura 18 • Pestaña Resumen

Nota: Escriba uno de los vol. de carril SERDES_VDDI disponiblestage como se muestra en la información sobre herramientas en la celda (Vol.tagcolumna e).

Figura 19 • Pestaña E/S

Nota: Desde SERDES_VDDI rail voltage se selecciona 1.5v (Figura 18), los estándares de E/S para SERDES_REFCLK ahora se pueden seleccionar desde el menú desplegable que coincide con el volumen del rieltage.

La Figura 20 muestra la sección Utilización del dispositivo que se muestra en la parte inferior de la hoja de trabajo Resumen.

Figura 20 • Sección de utilización del dispositivo

La Figura 21 muestra la sección Errores en la hoja de trabajo Resumen.

Figura 21 • Sección de errores

Sede Microsemi

Sede Microsemi

Una Empresa, Aliso Viejo,

CA 92656 EE. UU.

Dentro de EE. UU.: +1 800-713-4113

Fuera de EE. UU.: +1 949-380-6100

Ventas: +1 949-380-6136

Teléfono: +1 949-215-4996

Correo electrónico: ventas.support@microsemi.com

www.microsemi.com

©2020 Microsemi, una subsidiaria de propiedad total de Microchip Technology Inc. Todos los derechos reservados. Microsemi y el logo de Microsemi son marcas registradas de

Corporación Microsemi. Todas las demás marcas comerciales y marcas de servicio son propiedad de sus respectivos dueños.

Microsemi Propietario y confidencial UG0596 Guía del usuario Revisión 2.0

Documentos / Recursos

|

Software de estimación de potencia Microsemi UG0596 RTG4 FPGA [pdf] Guía del usuario UG0596, UG0596 Software de estimación de potencia FPGA RTG4, Software de estimación de potencia FPGA RTG4, Software de estimación de potencia FPGA, Software de estimación de potencia, Software de estimación |